## 11 3/11 UNIT-2 INTRODUCTION TO EMBEDDED SYSTEM Introducing Embedded System > This foreword begins with some personal philosophy about the development of embedded s/m. Philosophy: > & Some people walking along lake shores, and ficking up some stones of lodes. > One puson pides one stone which is small rounding flattists sort of rock, he says i'll bet I can make this rode skip five or every ten times over tender lake if & through. > Another puray takes big stone which round shape & which is like baskeliball. > Duother example sout stick- peyest for helping his non work since she getting older. of by each case they saw the objects from the ontside. - They sees only size, shape, color and possible uses. > This skipping a stone on river gives the or pushes the Emprove our designs. of Our anestors digging in the garden with sharpened Stiles didn't says is & think & need a shovel. - Some office people says why we dog by shorpened stide I invent a shovel so a can get this job

done genicles. > In this subject there are two main themes that will be intervovey through early the chapters a head. -> With each derign first look should be from the outside like its ochamous, what are the outputs, what are the constraints etc. -) Ar technology advances, we are able to do more and Embedded System deft: Embedded systems are a combination of www and she pacto, as well as other components that we bring together isto foroducts. Es: Cell phone, Music player, an aircraft guidance s/m Ay embedded system in ay electronic/electro-mechanic system designed to pulorm specific function & is a Combination of both hardware & software. > Embedded 2/m a techniques allow us to make froduct that are smaller, faster, more reliable, and cheapel - This is because of VLSI. > without VLSI embedded system would not be gearib & without embedded olm. SSI > Hundredo of Transistor is on clop 10-100 MS2-7 1960, hundreds of Premisshor - 1000

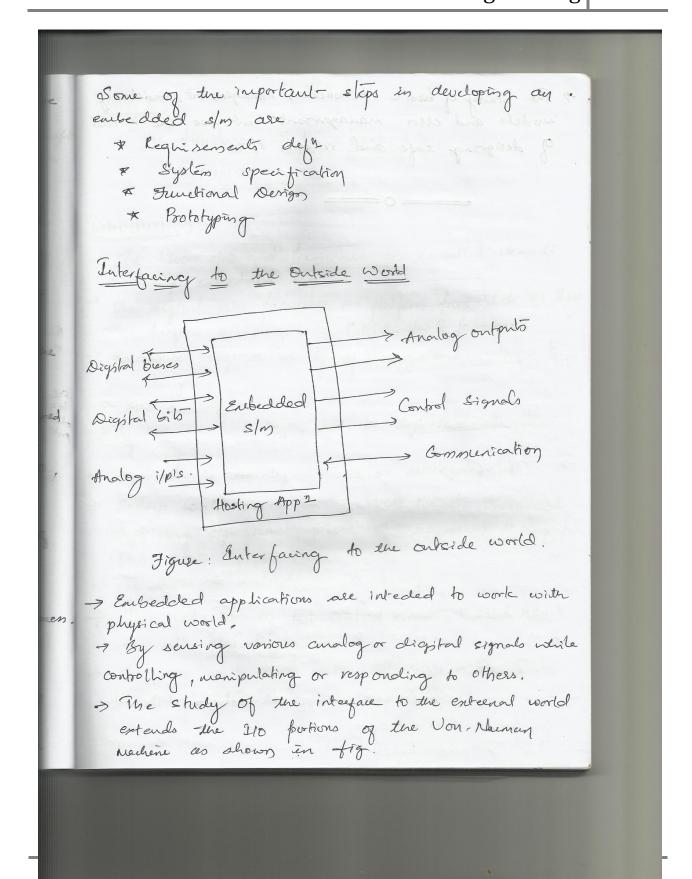

LSI -> 1970 (mid) -> 1000 transstor, 10,000 began in 1934 VLSI -7 1980 billion transistor. -> Embedded 2/m present a variety of challenges as we bring the how, are slow of the world ontside of the nicroprocessor together > A few years ago when musprocenors and PROM first appeared as new took, developing applications. - Proday we were ready desirining embedded applications Comprising thousands of Lines of code, multiple minoprocess-ors, VISI components & away logins that may be distributed around an office or around the world. > Valike the desktop PC, an embedded componler mustinteract with wide variety of analog and digital devices. -> The skilled embedded developed must know and anderstand the operation of sensor I transducers, AID conversion and were versa, etc building An embedded 1/m: > by addition to a wide variety of other hardware Components, we embed 3 basic kinds of Computing. engines Ento our s/m. i) Microcomputers, microprocessurs and microantroller. -> The Microcomputer & other how elements are connected wia the s/m bus

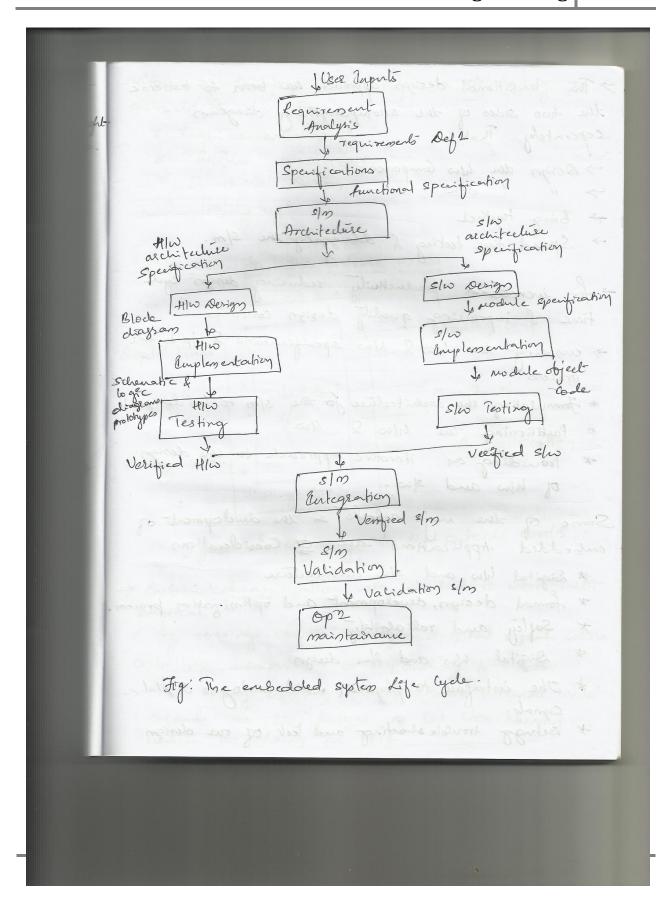

> The traditional design approach has been to travers the two sides of the accompanything diagram Seperately. That is > Derign the Ww Components Bring together -> Spend time testing & delongging the 5/m. -> for increased productivity, reducing during cycle time d'improving quality design contains \* ensuring the Www & slow sperifications & ilp to the \* Formulating the architecture for the s/10 to be design & Partitioning the 4100 & slw. \* Browding ay iterative approach to the design of how and sho. Some of the najor aspecto in the development of embedded Applications are of Considerations & Digital Ww and slw architecture. \* formal design, development and optimization pro \* Safley and reliability \* Digital Www and sho design \* The interface to physical world analog to degital \* Delagg trouble shooting and test of our design

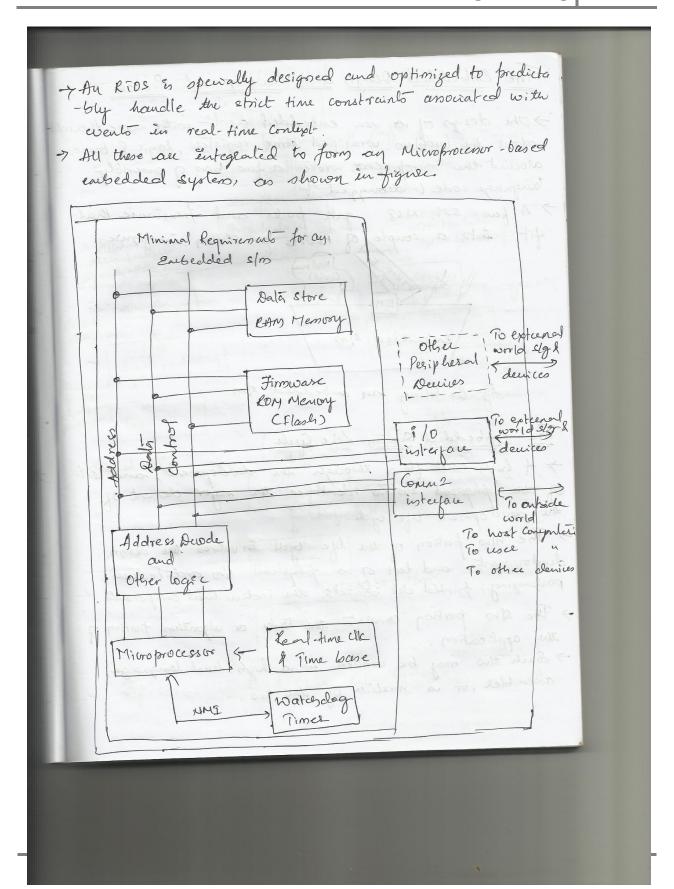

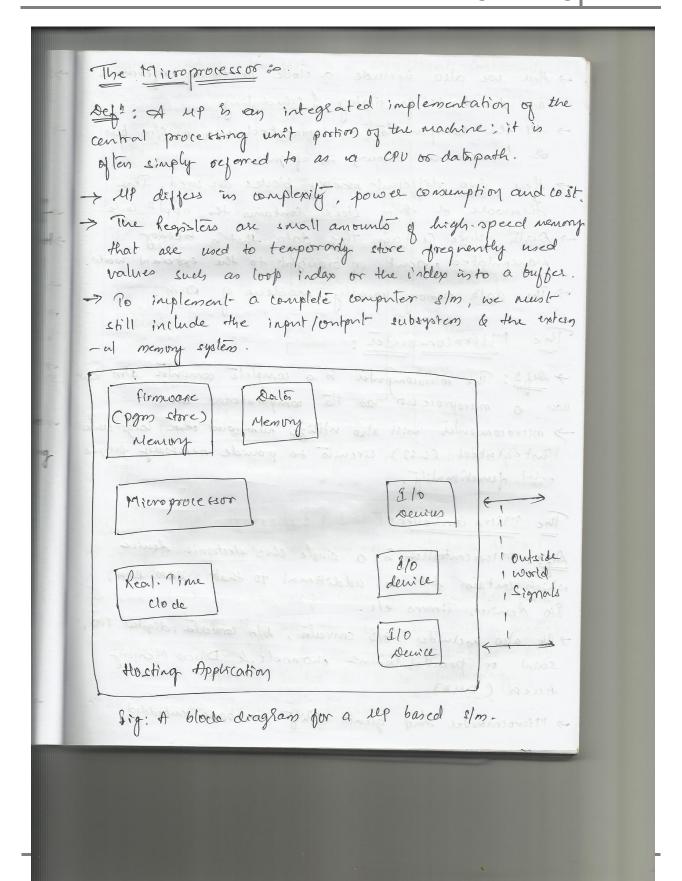

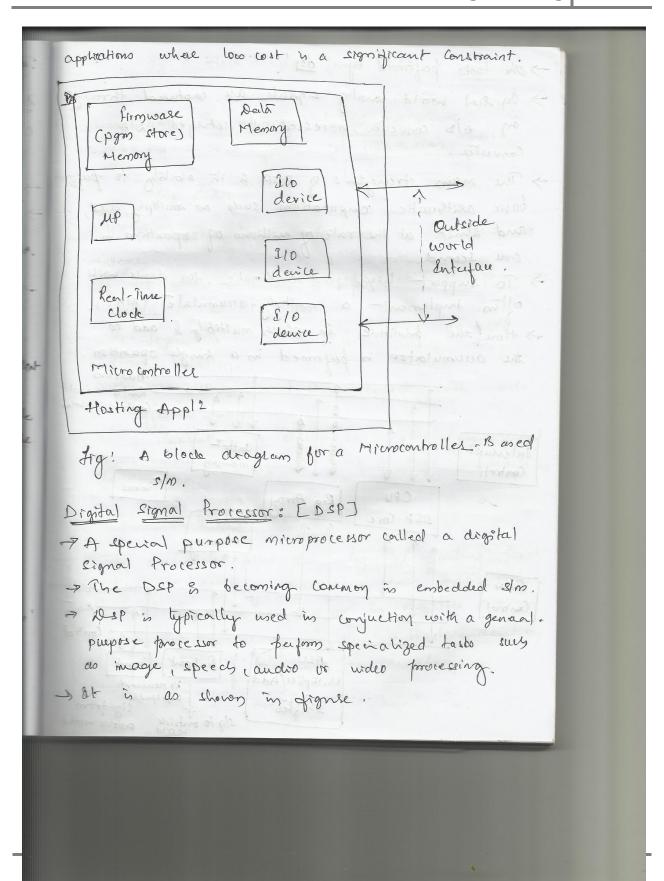

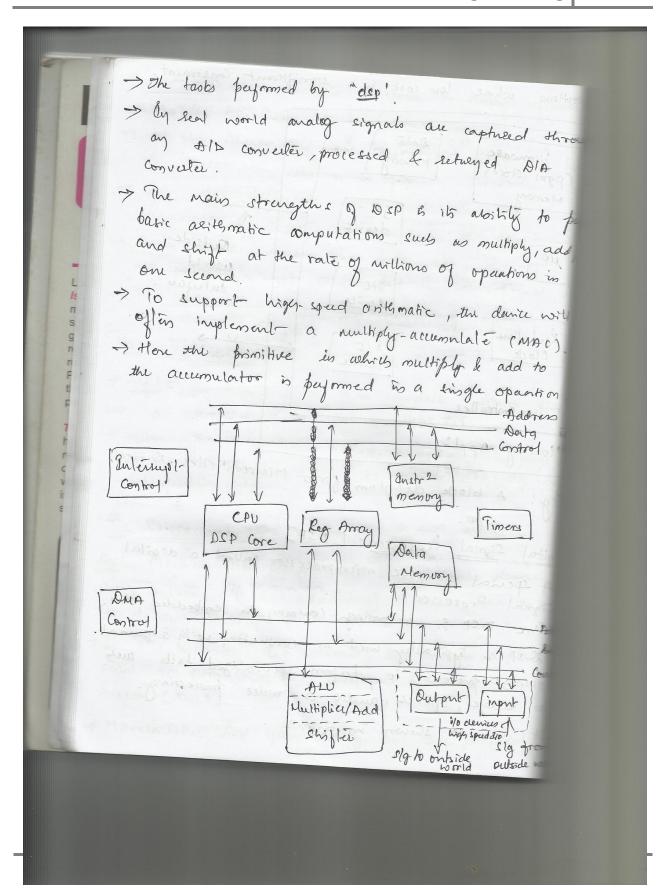

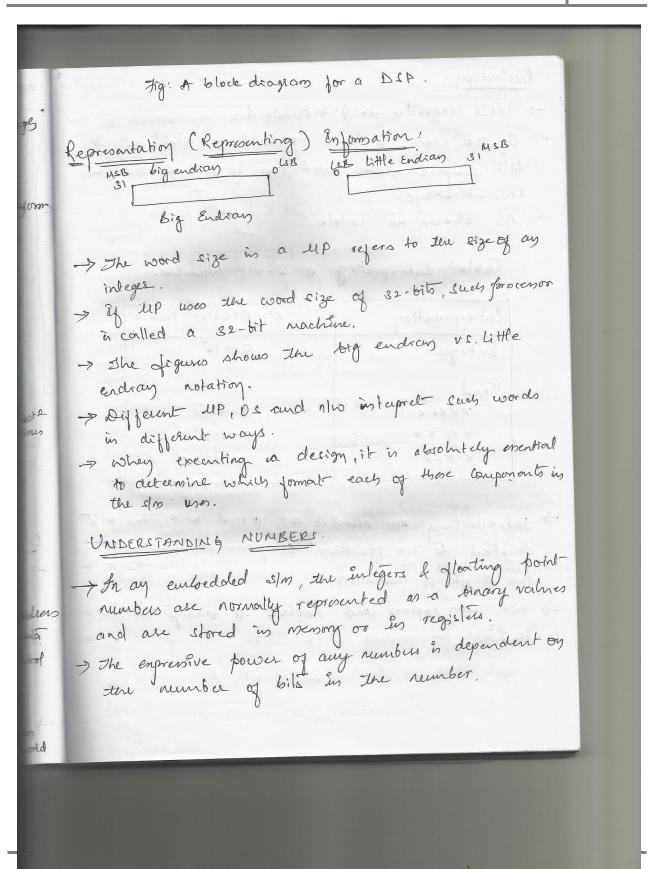

-) Here use also include a clock or timing referen as the basis for timing of scheduling. -> All the components are connected wa a s/m bu of busies as shown in figure. -> Here two different memory blocks are used. The Firmwork of pgm store contains the appl 2 code -> Data store Contains the data that is being manipulated, sent or brought to the extrend we > The data memory usually madeup of RAM. The Microcompuler: + Def 2: The microcompular & a complete computer s/m uses a microprocessor as 15 computational are. -> micro comporter will also utilize numerous other large. integrated (LSI) circuito to provide necessary pu - las functionality. The Micro Controller: Deft: tel sero controller & a single thip electronic device which contains MP is additional to that RAM, ROM 210 denico, Timers etc. 7 It also includes A/D converler, A/A converler, digital said or perallel comme channels. & Direct Memory Access (DMA). -> Microcontroller And great willy in basic embedded

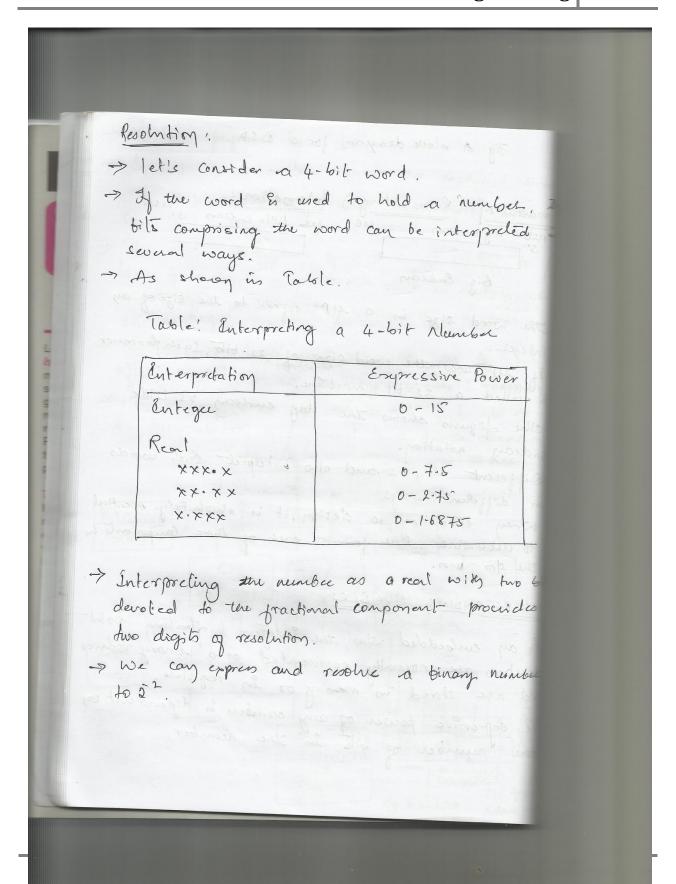

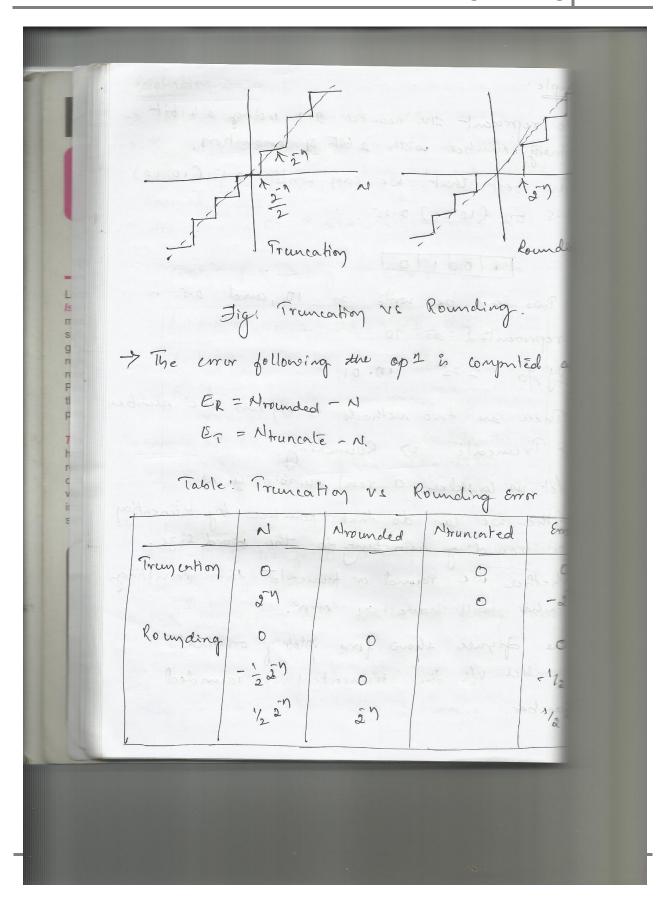

## Example: -> To represent the number 2.3 using a 4. bit binary number with 2 bits of roolnting, -> The best that we can write 2.5 (10.10) 2.5 or (10.01) 2.25 -> Two can be write as 10,4 and 0.5 is represented as 10. > 1ly for 2.25 10.0i. -> There are two methods to engress the numbers 1) Pruncate 2) Rounding. of Let us consider a real number in N. > Either we can do that rumber by truncation or rounding according to the word size. > Whether we round or fruncate the resulting number will have any error. -> The figures show for plot of original number v/s the truncated or rounded humber.

```

Truncation -2" < E7 50

Rounding -1/2 27 CER < 1/2 27

Propogation Error:

7 Here we are going to analyze how the

errors propagale under processing.

-> We begin with two numbers N. and N2.

-> Vader truncation The error is less than I least

significant bit.

Addition:

-> We can take the numbers with any error

NIE = NITE,

NZE = NZ+EZ

NIET NZE = (NITEI) + (NLTEZ)

· NI+NI+EI+EZ.

The error in rampling sum is in range

2.2 CET SO TO

-> Observe that the ramiting error is the sum of

the original Errors.

```

```

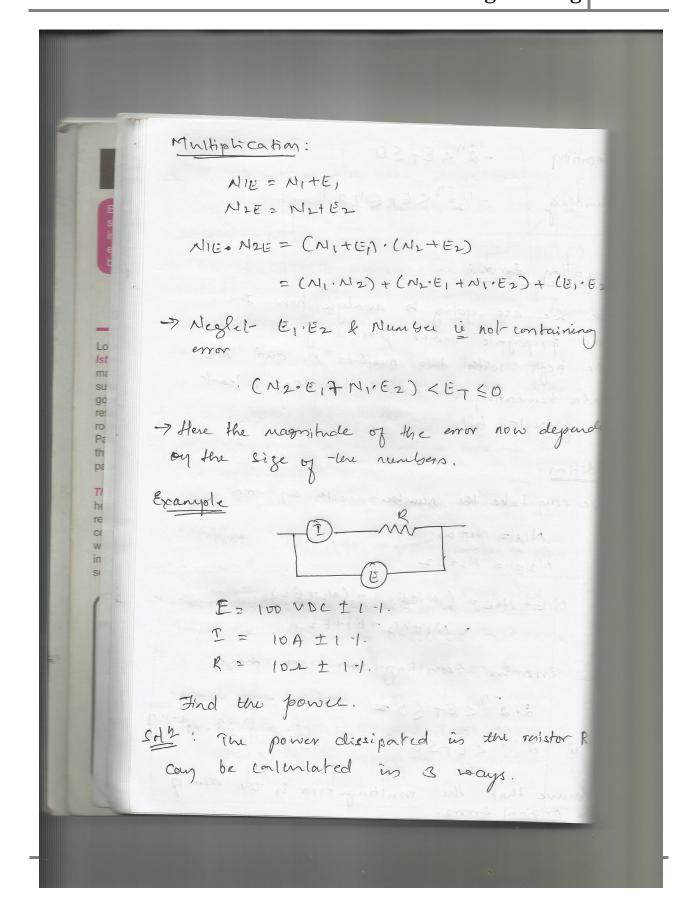

1> E1 = (100v ±11.). (10A ±1.1.); assorbed

= ((1000 ± 10 ×11.) ± ((100 × 11.) ± (11.11)))

= (1000 ± 1.1)

ES = 1000+1.1 or 1000-1.1

E2 > 998-9 > 1001.1 15

27. 32R: (10A±1.1.). (10A±1.1.). (10x±1.1.)

= [(100 ± 201.) ± 101. ± (11.11.)] [1011.1]

= (100 ± 0.2) . (10 ± 1./.)

2 ((1000±2)± ((100·11.)±(0·2·11.)))

£2R = 997 -> 1003.

3 \times E^{2} = (100 \times \pm 1.1.) \cdot (100 \times \pm 1.1.)

(10 \times \pm 1.1.)

2 (10000 ± 2), (11. ± 11.)

1999 1999 of (10± 1.1.)

```

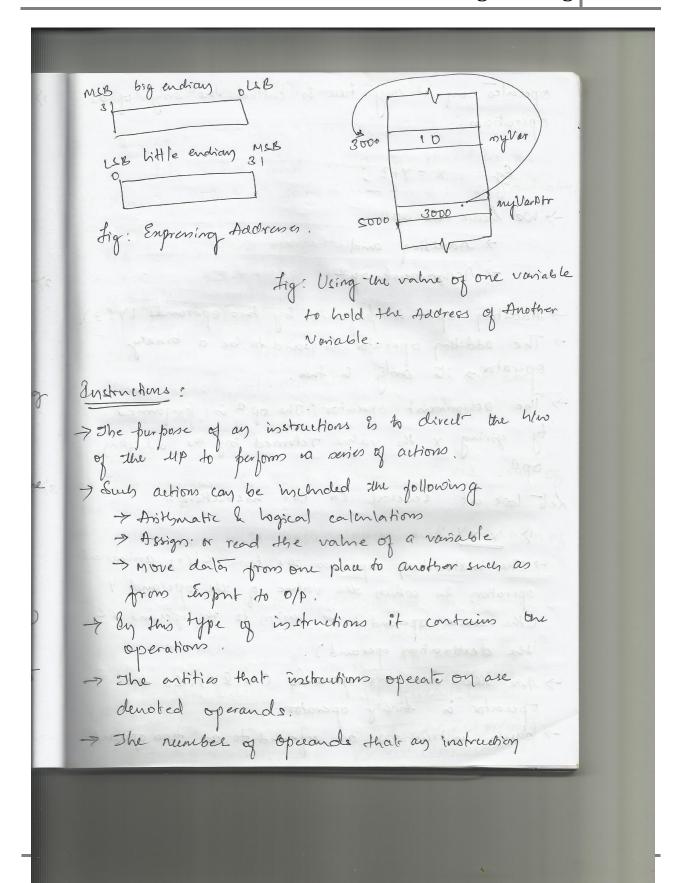

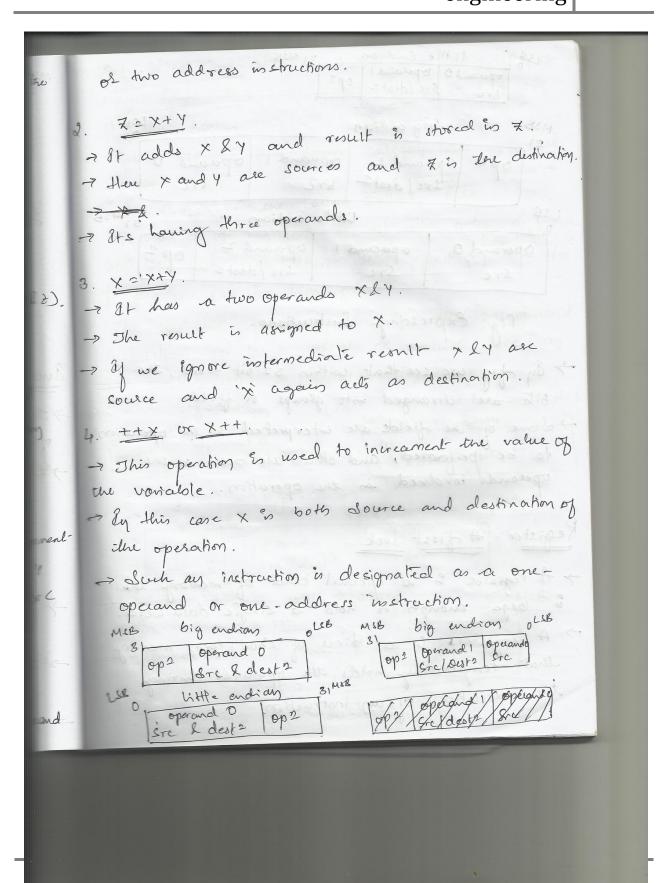

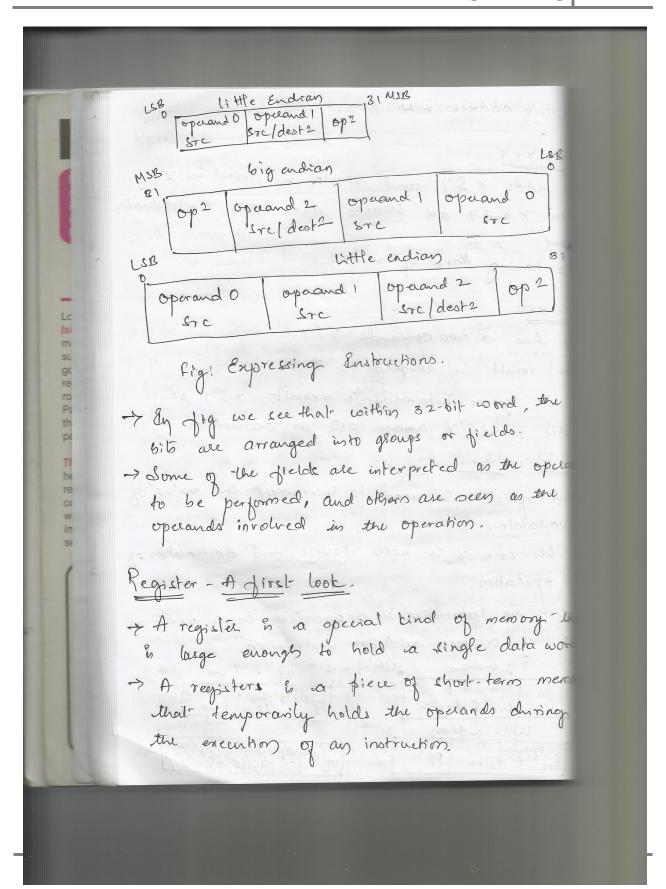

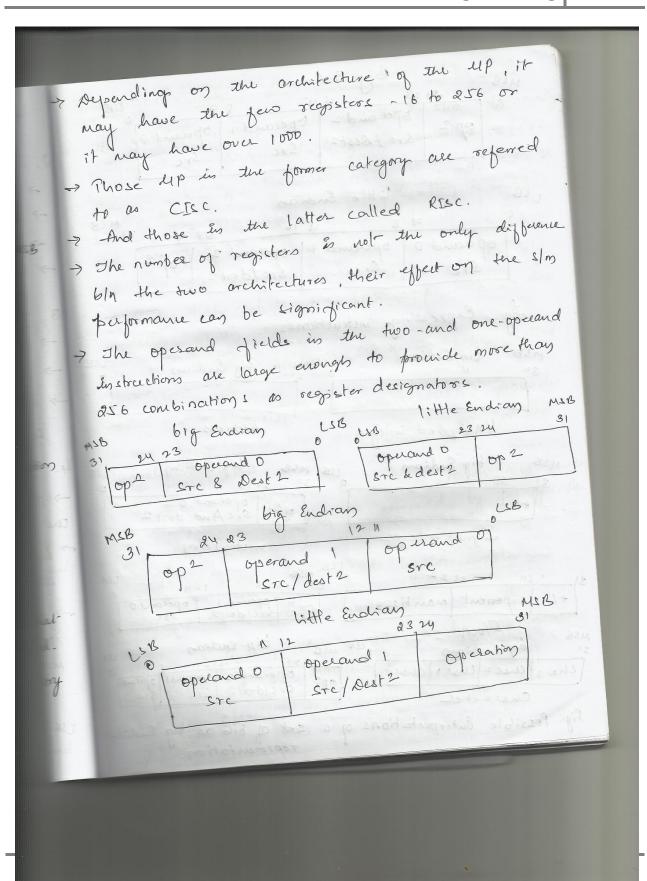

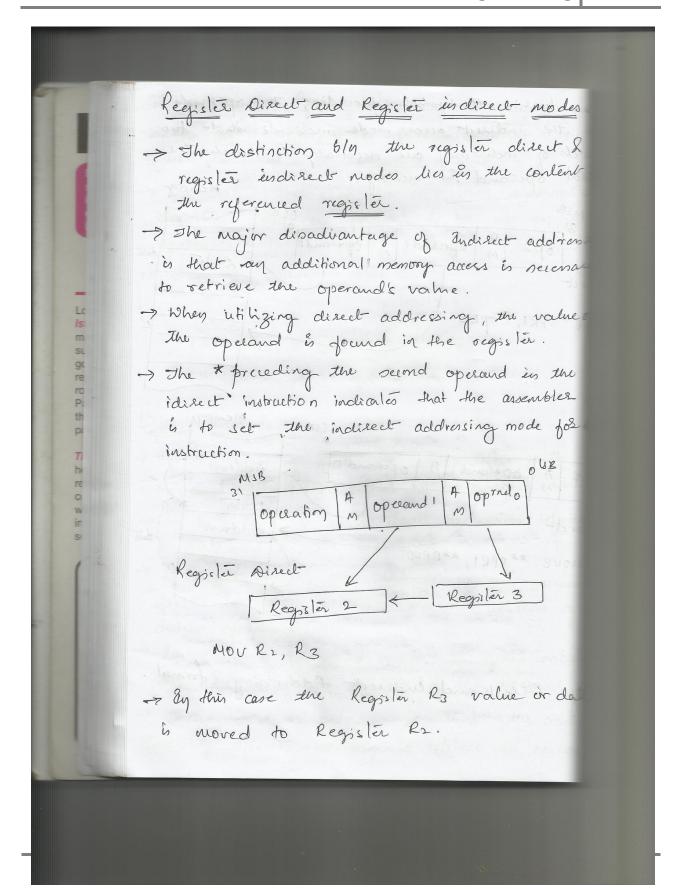

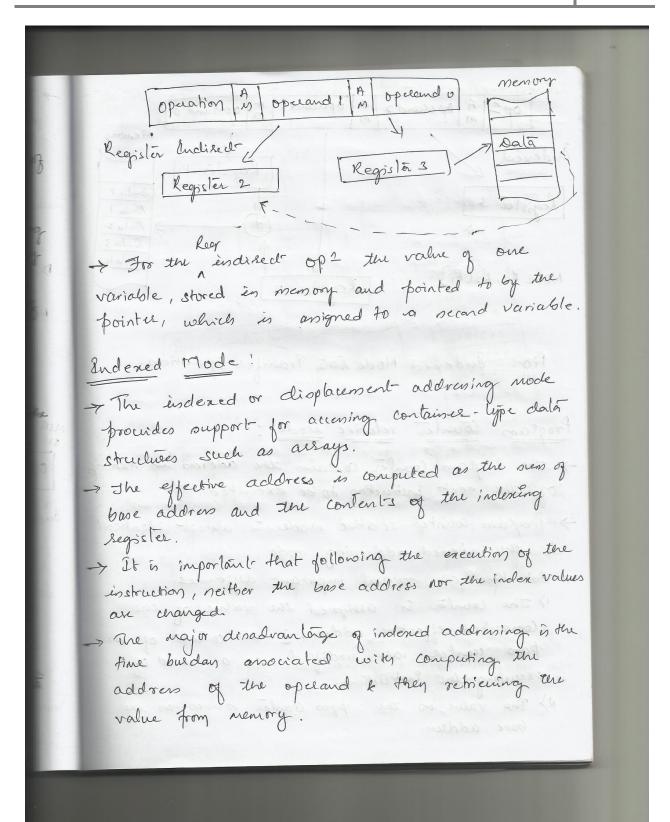

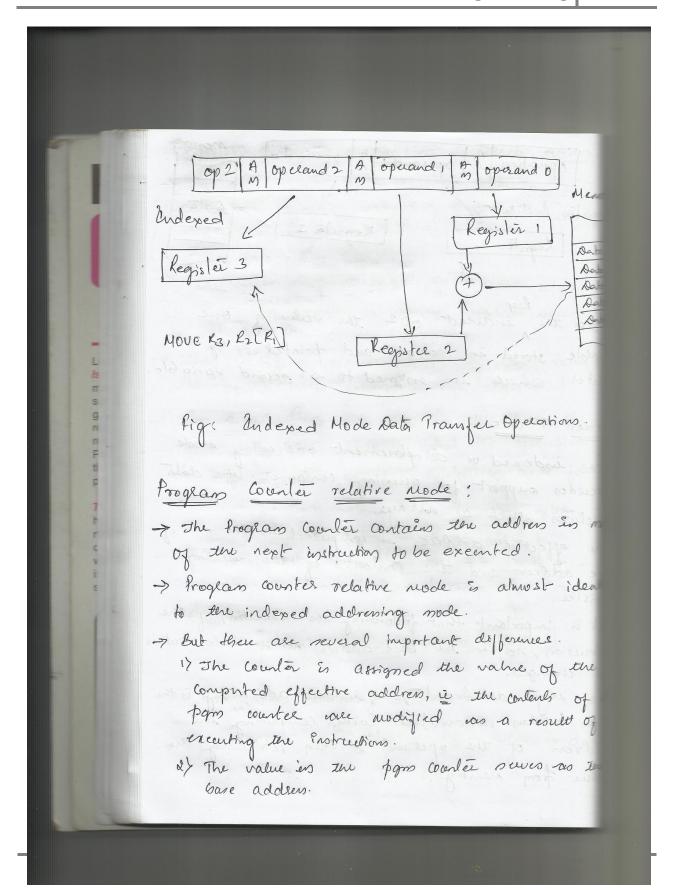

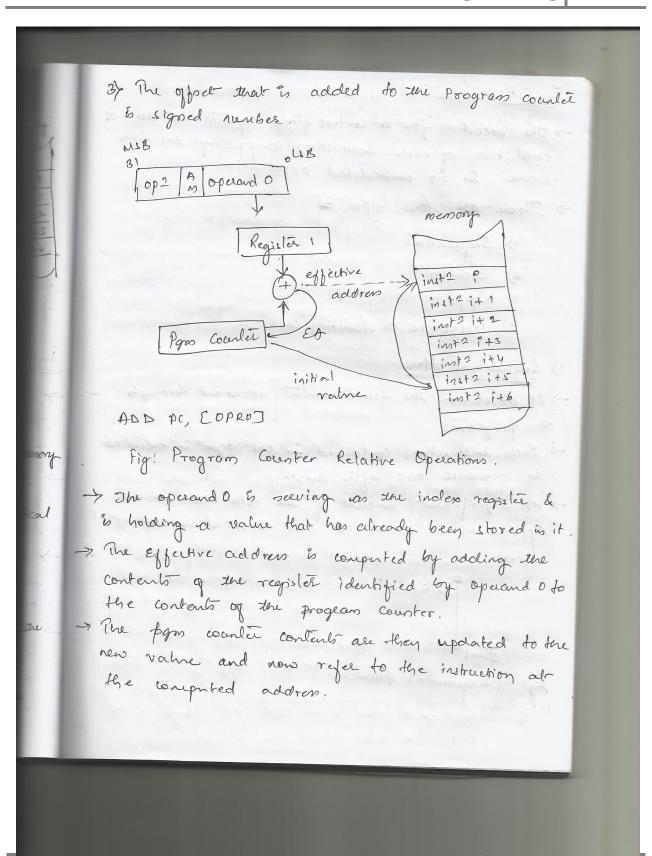

operates on at any time is called the only of operations. Eg: X=7+2; -> we have two up 2 ? Addition and > Assignment op 2. - Addition up 2 is payomed by two operands 1 -> The addition operator is said to be a binary operator, its only is two. -> The assignment operator: The op 2 is performe by giving x the value returned by the addit Lets look at several cor C++ instructions. 1) x=Y; -> The instruction expresses the basic cl(++ and operation In which the value of the operand (the source operand) is assign to the operand the destination operand) -> Here there are two operands (x ly). So the operator is sinary operator. -> duely instructions are referred to as two ope

MOVERI, #AH; 11 pnb 10-hex A- into RI MOVER2, #14+; // puts 20 - hex 14 - into R2 ADDR3, R1, R2', // Computer RitR2 & puts the roult into Rs. Fig. Assembler Segmential flow. 2) Branch: -> A boanching construct terminates a segnential flow of control with a decision point. de de cision point Jig: The Branch Construct. > At such a point, one of several alternal's paths for continued execution is taken based on the ont come of a last on some condition. -> The boands construct is used to implement an I else, switch, vo case statement. -> The branch may be executed unconditionally, is which case the contents of the PC are replaced by the effective address operfied by the operand - The conditional brancy is also executed.

-> The conditional information is temporarily h ias a collection of bits in flag registers of co Coole register.

E, NE -> operand , is equal/not equal to operand 7, Nt > The result of the operation is zero/not GI, GE > Operand i is greater than/grater than or a to operand 2.

LT, LE -> Operand: is greater the less than / less the egnal to operand 2.

V -> The Operation routed is an overflow. C, NC -> The " produced a carry / no cassy.

N -> The result of the operation is negative These are the some examples for the con Codes.

BR label -> Unconditional bounds to the sperifi BE label, BNE label -> branch to the spenfied labe the equal plag is set or not

BZ label, BNZ label -> branchs to the specified la if the zero flag is net or no

BGT label -> brands to the openified label if greater than flag is oct.

```

By label -> brances to the specified label if the overflow

flag is net.

BClabel, BNC label > branch to the specified label if the

carry glog is set or not set.

BN tabel > Granch to the specified label if the negative

glag is set.

These are some examples for the branching intractions.

CMP R2, R, 11 Compare R, with R2, will selv equal flag

BE $1 11 if the equal flog is och jump to $1

SUB R3, Ry, Soll Compute de la port rout in C.

BR $2 11 $2 is label created by Compiler.

$1; ADD R3, R4, R5 11 Compute die & put rouls

$2: ---

These are some example for Assemble. If else

Construct .

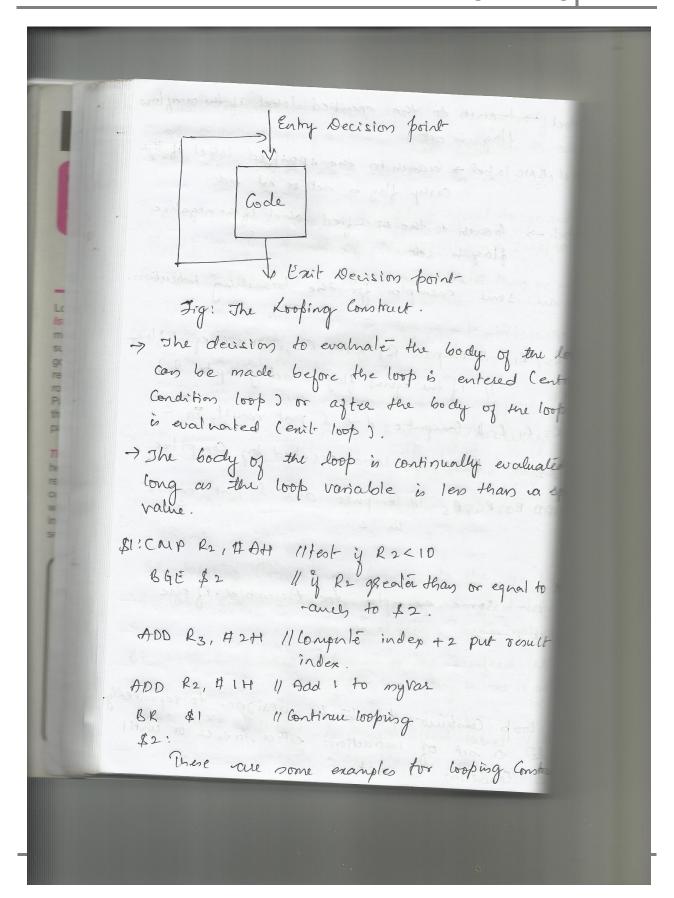

- The loop construct permits the designer to repeatedly

execute a set of instructions either frever or until

Some Condition is met.

```

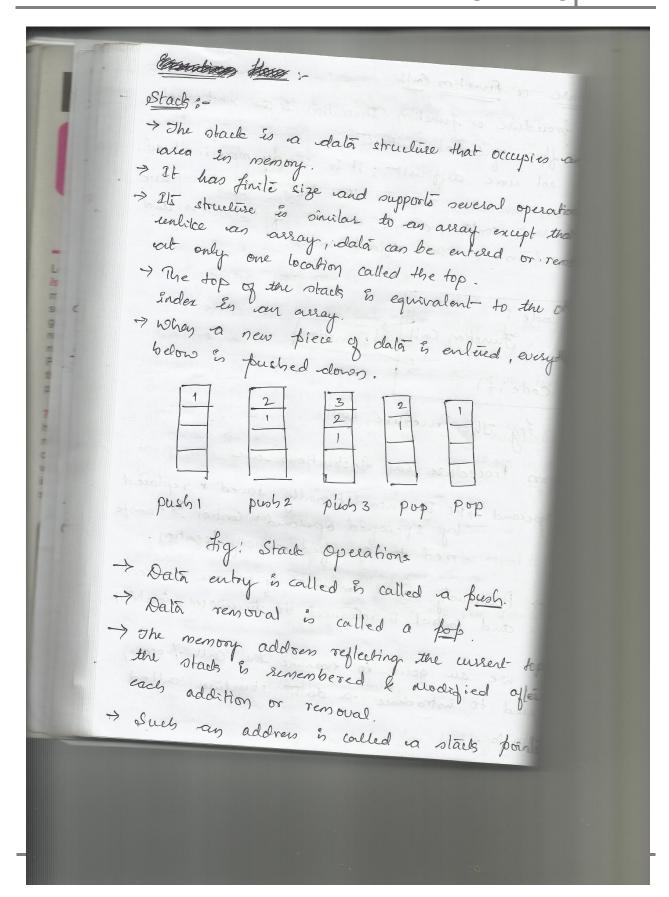

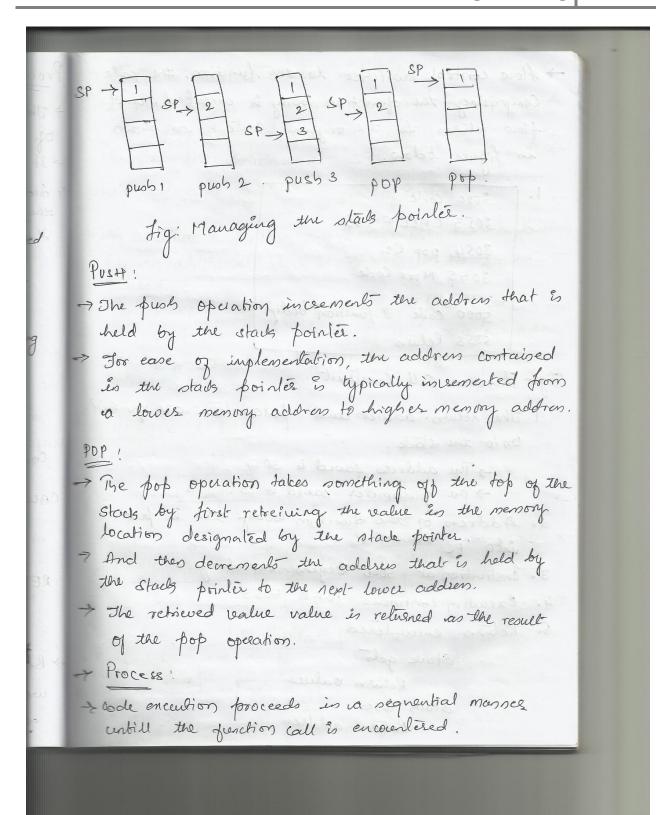

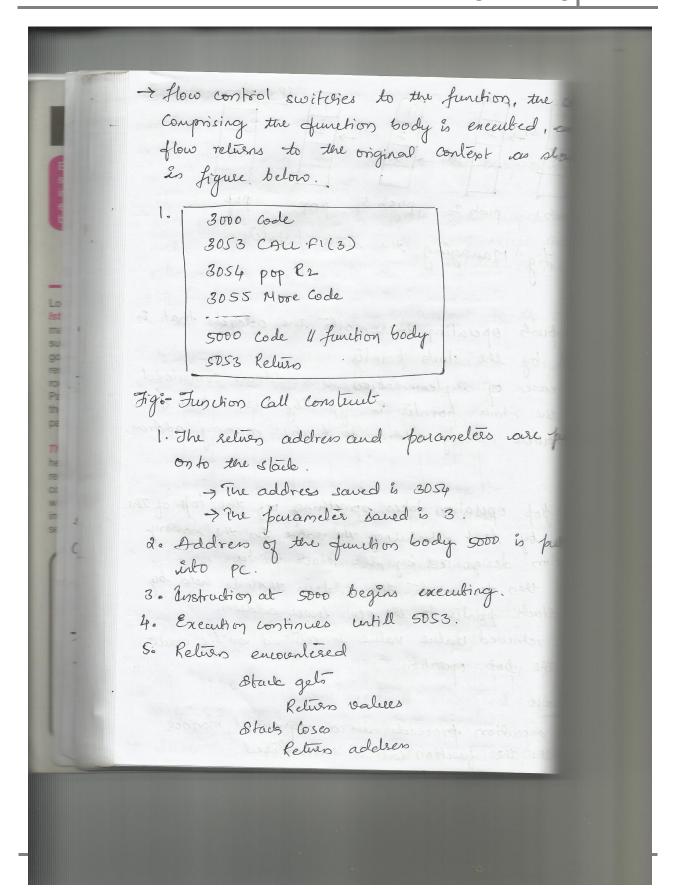

Procedure or function Call - The proceduse or function invocation is the most complex of the flow of control constructs. - It is not more difficult; it is simply more involved. of duch an invocation requires that the control flow leave the current context, execute a set of instructions and then return to the original context. Code i Function Call function Code it 1 Lig! The Procedure Call. Common Procedure Call Instructions are CALL operand -> PC is unconditionally sound & replaced by sperified operand; control is transfe - med to sperified memory location, RET -> Previously saved contents of PC are restored and control & returned to premious context. - Before we are going to examine the coll process, we need to introduce a dater structure alled a stacle.

```

4 multiplication

MUL

Division

DIV

11 intrement

DEC 11 devrement

Il operand tested & specified condition set

TESISET 11 atomic test and set:

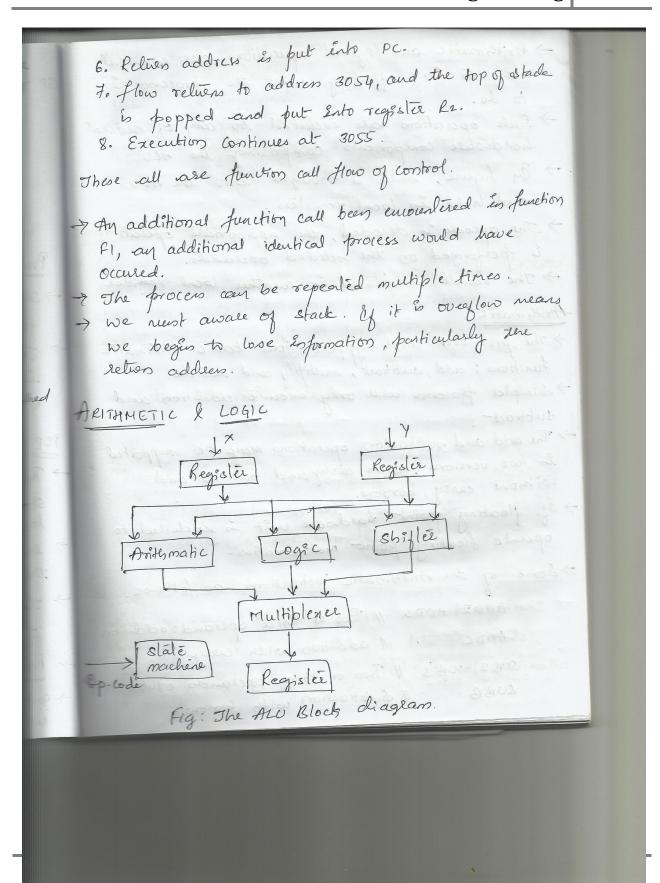

Logical Operations:

-> Logical operations performed interms of 0's and 1's

- Such operations are farticularly useful in embedded

applications where bit nanipulation is common.

of the example of logical operations as

below.

AND bitwise AND

OR bitwise OR

xOR bitwise exclusive OR

NOT or INV bitwise Complement

CLR or SET Clear or set

CLRC, SETC Carry Monipulation.

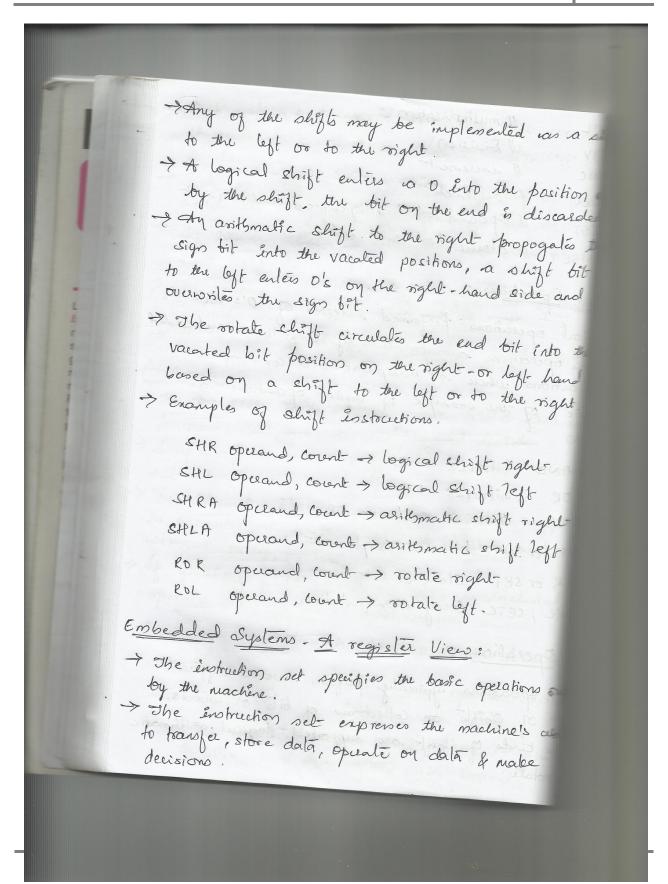

Shift Operations:

Shift operations typically perform several different tindo of shifts on collections of bits or words.

- Three birds of shift- are supported: logical caritymatic

action

```

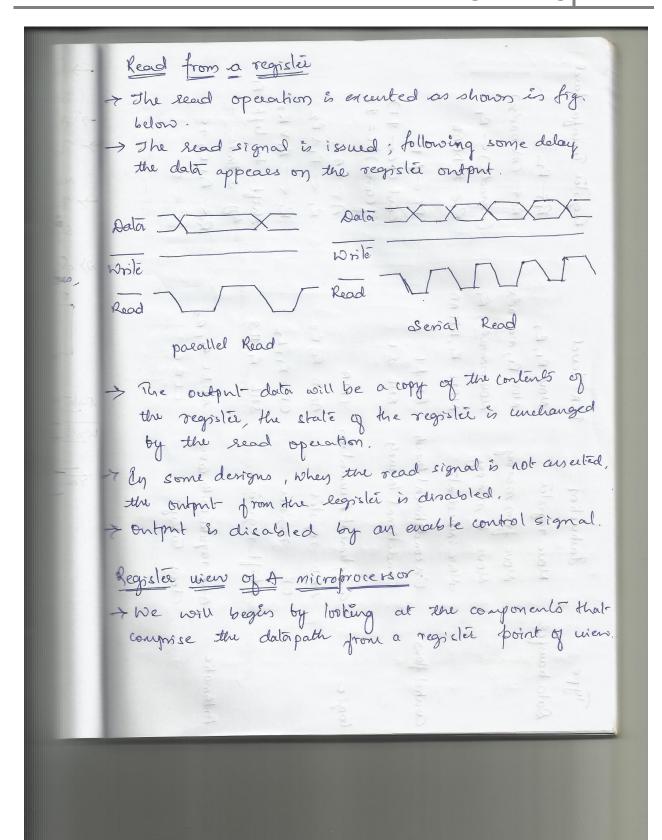

| Register Operations  Register Operations  Register operations  1> Read                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D'ile to la register  → A parallel write operation begins when the date                                                                                                           |

| placed onto the expuls of the registers.  > A delay to allow the data to settle on the the write signal is anosted.  - A serial write operation the signal nustraction accompany. |

| shows En fig below.                                                                                                                                                               |

| Read Read  Read  Parallel write Social write                                                                                                                                      |

| Fig. Worting to a Registers                                                                                                                                                       |

|                                                                                                                                                                                   |

|                                                                                                                                                                                   |

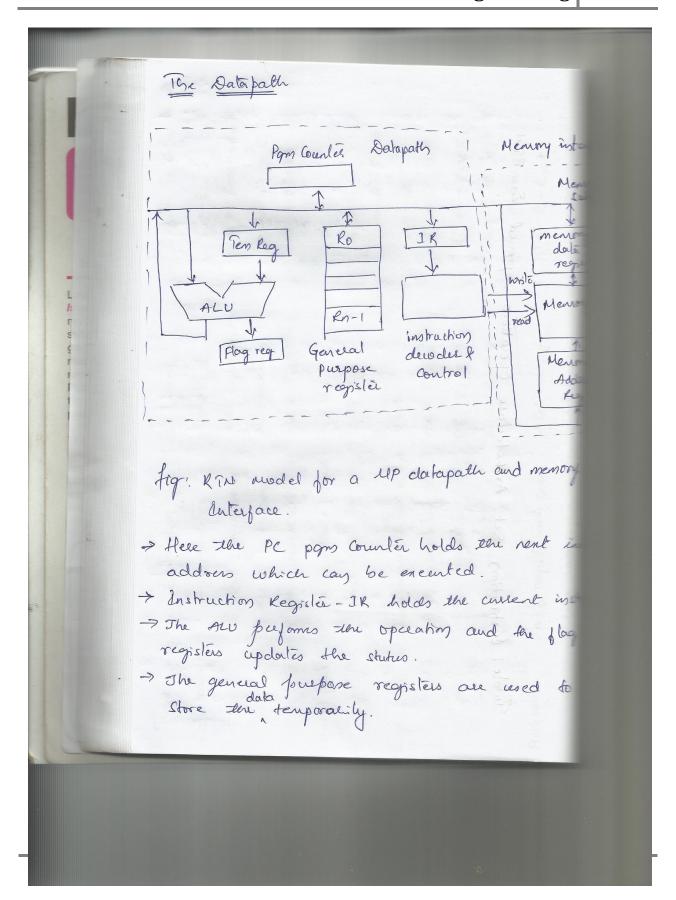

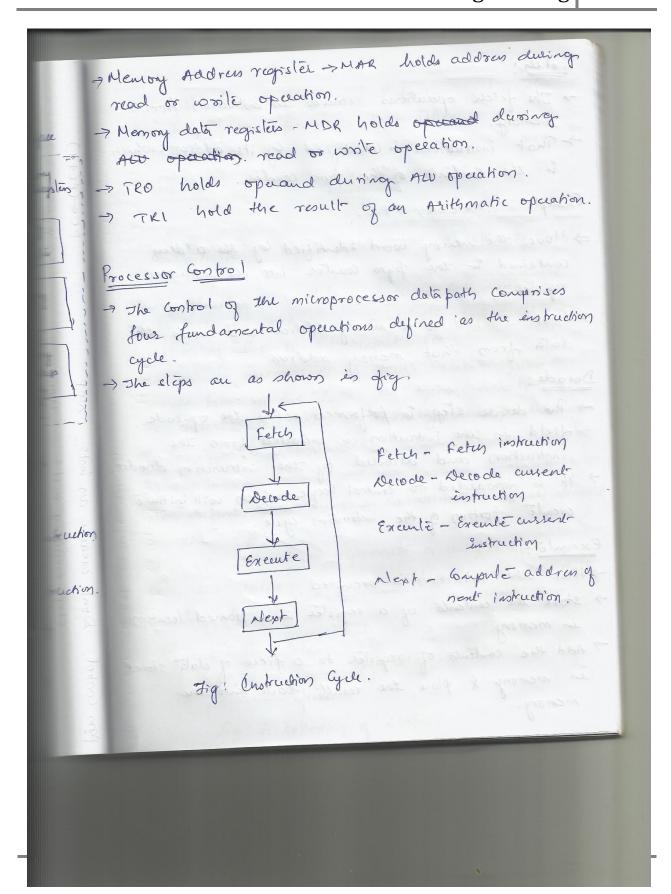

|     | Nept: - at will fetels the next instruction after the                                               |

|-----|-----------------------------------------------------------------------------------------------------|

|     | execution of the forcurous instrunction.                                                            |

| cs  | In a set of state vanadoles who state change with                                                   |

|     | The concept of State and Time.                                                                      |

|     | Time?                                                                                               |

|     | > A combinational logic system has no notion of time                                                |

|     |                                                                                                     |

|     | -> Here neglecting the delays through the system, we find that the output is immediate and a direct |

|     | gencion of the western input set.                                                                   |

|     | -> The whent output of a finite state system                                                        |

|     | depards both on the path the system rook 10 reach                                                   |

|     | the averest state and potentially, the present                                                      |

| du. | values of the input set.                                                                            |

| Ē   | State:                                                                                              |

|     | > State defines the status of an variables which fresent                                            |

|     | in the system.                                                                                      |

|     | - Early set of values represents a unique state.                                                    |

|     | - when the value of any valiable changes, the state                                                 |

| n   | a sim changes:                                                                                      |

| 4   | O initial O 2 coins.                                                                                |

| red | O 2 Coins.                                                                                          |

|     | Olight Ofinal                                                                                       |

|     | Lig: A collection of astates.                                                                       |

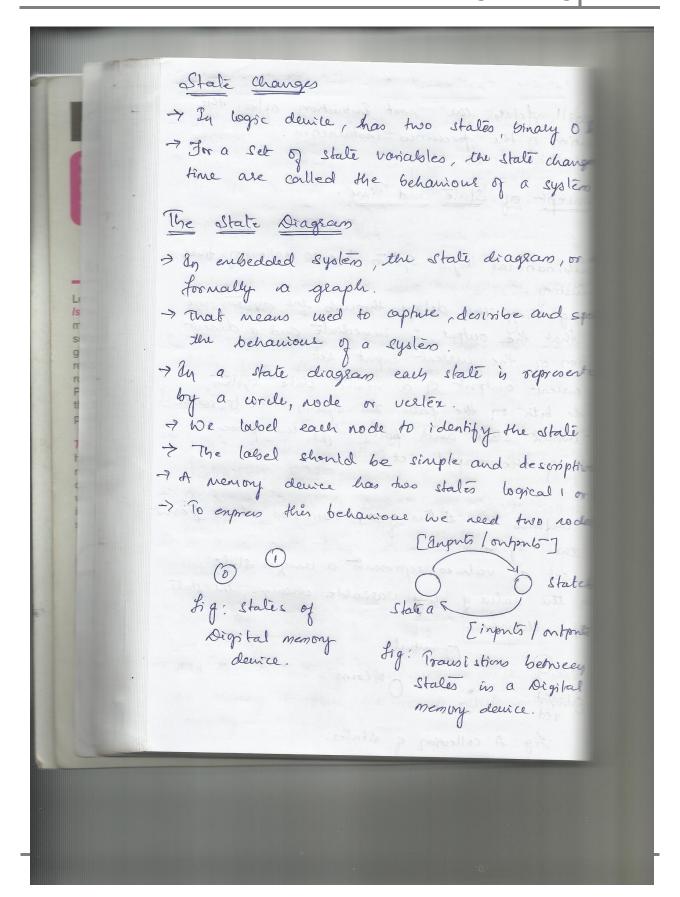

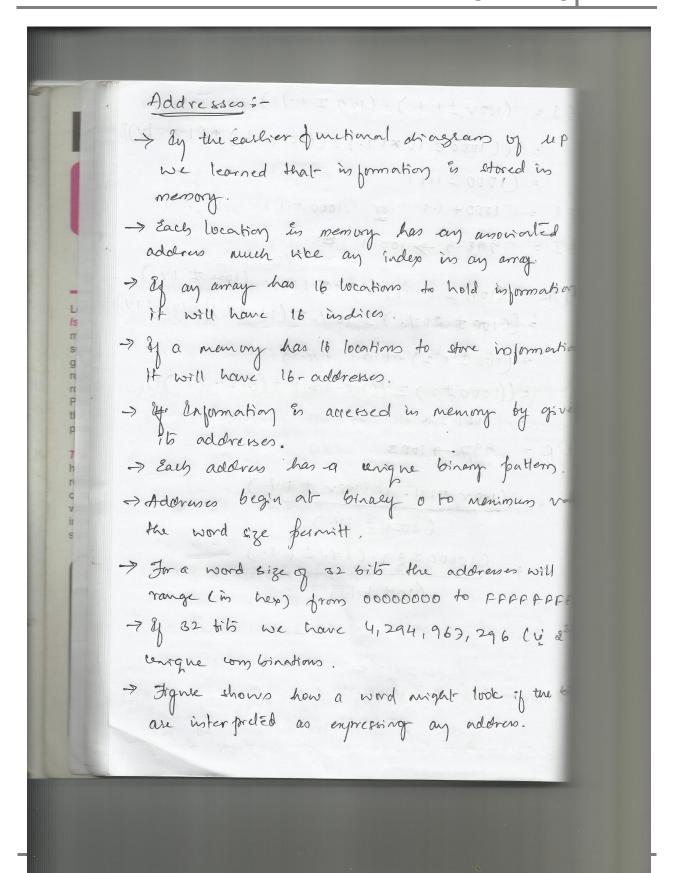

|     |                                                                                                     |